是什么推动了 PCIe 向Gen6发展?

在过去的PCIe几代发展过程中,PCIe 性能是由多种设备的发展所驱动的,包括:

- GPU

- NVMe 存储设备(SSD)

- 高速网络接口卡(NIC)

- 其他高速互连外设,例如USB-C 和 Thunderbolt

- 然而,随着Gen5 PCIe 的出现,我们看到较小范围的设备受益于速度的提升。

由于控制器和 NAND 闪存芯片的限制,大多数 SSD 不需要 Gen5 速度。Gen5 的优点是可以在使用一半数量的 PCIe 通道的情况下实现相同的速度。

同样,大多数 NIC 和其他外设可以从少量 Gen5 通道获得所需的带宽。

Gen5 和更高速度的主要驱动力现在来自游戏 GPU 和(最近)人工智能AI加速器的要求。在这两种情况下,通常使用 PCIe 插槽的完整 16 个通道,因此进一步提高性能需要升级到下一代。

到 2023 年下半年,我们看到了引入 Gen6 系统路线图的巨大推动力,多家公司计划在 2024 年发布重大开发版本。对 GPU 计算能力的需求几乎完全由人工智能发展驱动。总线速度加倍将给人工智能公司带来重大好处。

速度变化

Gen5 PCIe 的推出每通道的最大理论带宽为 32 GT/s(每秒千兆传输)。这相当于每通道大约 4 GB/s(每个lane)或 x16 连接的 64 GB/s。

PCIe Gen6 更进一步,将带宽再次加倍至每通道 64 GT/s。这意味着每个方向上每个通道的速度约为 8 GB/s,对于 x16 设备而言,速度可达惊人的 128 GB/s。

请注意,这是“理论”带宽,由于协议的开销,实际性能会较低。

信号变化

- PAM4

Gen5 PCIe 使用具有2 个电压电平的 NRZ 信号,表示二进制 0 和 1 。Gen6 使用更复杂的 PAM4 系统,有 4 个电压电平。Gen5 和 Gen6 具有相同的 16 GHz 基频,但由于采用 PAM4 编码,Gen6 的抗噪能力仅为 Gen5 的三分之一,因此需要更严格的设计容差。了解 NRZ 和 PAM4 信令 - 前向纠错或FEC

这是协议的新增内容,用于纠正传输中发生的较小错误,而无需重新传输数据。与第 5 代相比,这些额外的错误恢复数据增加了额外的开销。 - 流量控制单元(FLIT)

Gen 6 PCIe 引入了新的数据传输结构以及 FEC,以减少开销并实现更快的数据传输。这将需要新的解码系统,并且与第五代相比是一个巨大的变化。

电源效率

新的节能状态允许一些PCIe Lane通道关闭,而另一些PCIe Lane通道继续运行。这样可以在负载变化时实现可扩展的性能,同时最大限度地减少功耗。新的电源状态称为 L0p

连接器变化

市场上已经有适用于 AIC(插槽)设备的 Gen6 连接器。

适用于 E1、E3 和 CXL的现代EDSFF 连接器预计也将在 Gen6 版本中提供。

鉴于该连接器较旧的性质以及 SSD 上 Gen6 的优势较低,SFF-8639(用于 U.2 和 U.3 驱动器)很可能不会进入 Gen6。

板级布线设计带来的挑战

Gen6 信号对于板级走线和布线将是一个重大挑战。FEC 将有助于恢复较小的错误,但转向 PAM4 将显着减少系统中的 SI(信号完整性)开销。这将使数据容易因丢失和串扰而出错

- 损耗

Gen6 的总插入损耗预算为32dB,低于 Gen5 规范中的 36dB。这是一个很小但很重要的变化,将限制走线的长度和转换的数量(连接器和类似的) - 串扰

这是从一个通道到另一个通道的干扰(串扰)。使用PAM4,干扰更改数据位的可能性显着增加。这使得PCIe Gen6的串扰风险更高,需要更复杂的设计来缓解。

Gen5 与 Gen6 PCIe 兼容性

与前几代 PCIe 一样,保持了向后和向前兼容性。旧设备应在新的 Gen6 插槽中运行,而 Gen6 设备在放入旧插槽时应降低速度。向后兼容性的要求显着增加了 Gen6 硬件的复杂性,特别是SerDes,它必须支持 NRZ 和 PAM4 编码并在运行中在它们之间进行切换。

测试工具和测试环境搭建

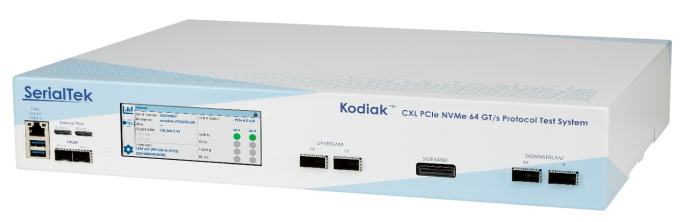

- SerialTek作为业内领先的协议分析仪厂家,已经推出了PCIe Gen6协议分析仪,训练器,可以模拟PCIe Gen6 RC(CPU端)以及EP(各类device controller插卡),以及针对协议的兼容性测试套件CTS

- Quarch 正在努力开发Gen6 产品,因此当您拥有原型设备时,我们应该准备好用于功耗分析和热插拔/故障注入的测试解决方案

- SanBlaze将于2024年下半年将推出支持PCIe Gen6 SSD和SSD卡的测试设备

- SerialCable将于2024年将陆续推出支持PCIe Gen6 SSD和插卡的各种Switch卡,retimer卡,测试盘柜,转接,延长线,转接延长线等等服务PCIe Gen6信号品质的搭建PCIe Gen6测试环境所需的基础组件

-

PCIe Gen5在过去2年在国内的发展回溯和总结

注意:下面是2021年底/2022年初针对PCIe Gen5在国内和国内发展的一个回溯

随着高速计算机设计,GPU,DPU,MaPU,SSD,SmartNIC, 高性能网络,存储,以及AI人工智能等技术的发展,系统内部或者外联基本都是通过高速PCIe总线互联, 本文档专注于探讨美国、欧洲以及中国业内公司广泛使用的针对PCIe Gen 4/5协议诊断、分析、测试工具以及测试环境搭建过程中用到各种工具,尤其是针对基于PCIe Gen 4/5高速总线开发测试所用到的各种工具的图解剖析,相信读过本文档可以帮助你解决PCIe Gen 4/5测试工作中可能遇到的大部分疑问。

首先,我们从和全球知名的PCIe和NVMe SSD测试工具厂商的交流以及他们的销售统计来看一下全球PCIe Gen 5研发面临的挑战和趋势。

Saniffer合作的全球知名的四家PCIe/CXL/NVMe测试工具厂商,即SerialTek, SanBlaze, SerialCables, Quarch大概从3年前开始都陆续发布PCIe Gen5相关的产品,通过最近和这些厂商的密切沟通交流,以及和国内客户的沟通,针对Gen5产品开发我们发现存在下面几个挑战和趋势:

1)PCIe Gen5诊断分析工具存在很大挑战

其实这部分调整不仅仅体现在测试工具上面,同时也体现在下述涉及的搭建Gen5测试环境。在研发阶段,不仅需要高性能的示波器,对于大部分芯片开发来讲也需要PCIe Gen5协议分析仪。众所周知,协议分析仪必须将对应接口的interposer串接在链路中间,由于Gen5对于信号的高要求,目前这种机制已经带来了大量的问题,包括建链不成功,无法复现故障,抓不到数据,抓到的全是错误,等等。据SerialTek公司VP介绍,在美国,自从2021年下半年起遇到大量客户涌入要求试用Gen5分析仪,这其中包括不少前期已经购买了Gen5分析仪的公司,这从侧面间接也说明了信号问题的严重性。在国内,我们从客户端也发现了一样的问题。

2)PCIe Gen5测试环境搭建成为目前的突出问题

目前Intel仅提供桌面级的Gen5 CPU,几个主要的主板厂商的Gen5 x16插槽信号质量都不大好。我们大概两个月前购买并测试了A厂商的产品,Gen5 x16 host card插入其唯一的Gen 5 x16 slot只能和Intel Gen 5 CPU协商成Gen 3,大概2周前A公司发布新的BIOS,升级后总算可以协商成Gen 4。B公司产品到目前为止也仅能协商成Gen 4。总体来看,两台设备的Gen5插槽信号质量堪忧。

一些前期的Gen 5用户,采用转接卡进行转接的时候信号质量出现严重衰减。Gen 5对于PCB板材,过孔,接插件的要求非常高,并且目前在全球物料短缺的情况下很多物料很难买到。PCIe Gen5的信号质量成为一个突出问题,尤其是涉及到转接,延长等问题的时候。这个在Gen 5问题诊断的时候给用户带来了极大的挑战。国外一些专家甚至建议在采用PCIe Gen 5系统设计的时候每隔一个比较短的距离就增加一个Gen5 retimer。

3)PCIe Gen5 SSD的接口选择的趋势

下面是Saniffer公司和Quarch CTO在2021年12月底沟通的总结:

Quarch在2021年全年各类产品出货中,各种接口的测试模块的顺序如下:

Gen 4 NVMe SSD测试模块出货量最大的是U.2, 其次是U.3和EDSFF (E1)。

Gen 5 NVMe SSD测试模块,目前出货量最大的仍然是U.2, 其次是EDSFF (E3) ,后面才是U.3。Gen 5 插卡模块也很受欢迎,主要用于芯片等验证卡的早期产品测试,例如芯片早期bring-up等测试。根据目前的趋势来看,2022年U.2和EDSFF E3将增长非常迅速。EDSFF接口总体上将非常快的受到市场的欢迎。

另外,根据我们和SanBlaze VP的沟通,目前SanBlaze大量出货的PCIe Gen5 RM5默认配置就是16个Gen5 E3.S插槽(对比Gen4 RM4默认配置是16个U.2插槽)。同时,我们也看到一些存储系统业界主流厂商基于Gen 5 NVMe SSD的首发全闪存阵列也多采用E3.S。还有,国内目前开发企业级NVMe SSD的公司很多都从我们公司购买了SerialCables公司的EDSFF各种转接卡和线缆。这些都从侧面印证了EDSFF会在2022年会获得不错的进展。

针对电源拉偏测试设备PPM(Programmable Power Module),销量按照U.2/U.3, EDSFF, AIC和M.2依次递减。

当然,如果考虑到M.2在低功耗状况下各种问题的分析,针对电压/电流/Sideband Signal的实时和回溯分析监测产品PAM(Power Analysis Module)对于客户的吸引力显然更大,使用PAM进行问题分析的效率大大超过了使用示波器,Keysight后者吉时利Keithley传统电源类产品的效率,成为目前业内分析M.2低功耗问题的首选设备。

国内主流的M.2 SSD厂商、系统商(如笔记本厂商),以及第三方政府评测机构都大量采用这PAM设备做问题故障分析和横向对比评测。

4)国内领先的公司都在2022年开始PCIe Gen 5项目

这个不仅仅体现在SSD controller的drive盘领域,同时也涉及到其它各种需要使用高带宽的芯片和板卡设计领域。区别仅是2022年上半年还是下半年而已。

PCIe Gen4/5/6协议分析和诊断碰到的难点

信号问题

由于PCIe 3.0链路速度为8Gbps,信号质量问题还不是特别突出。但是,PCIe 4.0 (16Gbps),PCIe 5.0 (32Gbps),PCIe 6.0 (64Gbps)对于分析仪的interposer设计提出了很大挑战。PCIe协议分析仪的架构决定了如果要抓取链路的双向数据,必须依靠相应接口的interposer串接在链路中间。例如,参见下图,如果要分析U.2 NVMe SSD,那么就需要一个U.2 interposer串接在U.2背板和U.2 SSD中间,interposer的设计目标是不影响双向数据交互,同时将双向信号各分出一路信号送到“旁路”的PCIe协议分析仪前面板的upstream和downstream端口,upstream和downstream端口在机箱内部分别连接到一块抓包分析板,将收到的ordered set或者packet打好时间戳、格式化好以后写到内部的高速buffer缓存。

图 2 30

但是,真实的interposer产品,由于设计、架构等方面的原因,对于16Gbps、 32Gbps、64Gbps的高速信号往往非常容易在串接interposer后导致各种问题。

解码速度

PCIe Gen3时代时候的协议分析仪一般的抓包buffer在4.5G, 9G, 18G, 36G等,但是PCIe Gen4/5/6由于速度提高了2倍,4倍,相应的分析仪的buffer最低都在36G, 一般配置72G, 144G, 288G。如果分析一些Gen4 或者Gen5 x16,一般都是建议配置最低144GB buffer,因为即便这样在双向流量较大的情况也仅能抓取很短时间的数据。

我们以PCIe Gen 4 x4为例,即16G x4 = 64G,如果双向打满流量(Read/Write: 50% / 50%)的情况下的理论吞吐量大概为64G * 2 = 128Gbps(约12GB/S, 128/130bit编码)。由于协议分析仪抓包的时候需要加上时间戳(timestamp)以及很多其它格式化信息(例如标识Packet是否有CRC Error),所以实际占用的buffer远比我们链路上传输的数据要大,基本上读/写压力同时加上的话,几秒钟几十个GB字节。但是这对于PCIe Gen 4/5/6 协议分析仪的Trace解码分析速度和文件保存速度带来了挑战。

市场上见到的传统的PCIe协议分析仪,包括所有除SerialTek之外的Gen 4/5/6分析仪,都是一种嵌入式架构,可以简单理解成和一台传统“打印机”或者“投影仪”架构类似,分析仪硬件的主要功能只是抓取双向数据,之后需要通过两个步骤才能实现协议解码。

第一步,通过分析仪内部嵌入式CPU(一般都是几百Mhz)将数据传输到协议分析仪软件,一般使用网口或者USB,这个过程由于受制于分析仪内部较弱的CPU限制往往传输速度非常慢;

第二步,协议分析仪软件进行解码显示,这个过程由于都是通过程序单线程进行解码分析会非常慢,同时由于处理上百GB的数据的时候受制于电脑内存(例如笔记本的内存通常为16GB)的限制会在内存和硬盘之间来回“倒腾”数据,所以很慢。总之,用户的体验很不好。实际测试结果:传输32GB数据大概需要4小时,解码还需要4小时,需要8个小时才能看到完整解码。如果解决一些读/写不一致的问题,那么可能要抓取尽量多的数据,例如100GB数据,即便电脑和分析仪软件不崩溃的话,可能需要48小时以上才能看到解码。这对于好不容易复现一个问题,然后再进行问题分析来讲,效率非常低。

对于PCIe Gen 5 x16而言,双向打满数据,大概为32Gbps * 16 lane *2 = 1TBbps(约100GB/s),所以,buffer大小为128GB的分析仪还无法抓到1秒钟数据,所以处理这些大的数据的能力就成为考虑协议分析仪的一个非常重要的方面。

SerialTek公司的创新设计的PCIe Gen4/5/6协议分析仪采用高性能server架构,所有解码等工作都在分析仪内部完成,解码完毕后直接将通过Web界面展示到客户端的Chrome等浏览器,有点类似于视频会议Webex/Zoom/腾讯会议等,占用带宽只有20KBps,所以解码显示非常快,早期的Gen4协议分析仪解码144GB字节基本1秒钟即可完成,当然Gen5/6协议分析仪停止抓数据后会有一个post-process预处理过程稍微需要一点时间,后处理完毕后工程师可以在解码界面上直接拖动到最后一行查看解码,如果需要重新抓取数据,下一秒即可开始。

SerialTek PCIe Gen 4/5/6协议分析仪的革命性设计

SerialTek总公司为位于瑞士的Ellisys公司(Made in Switzerland),但是其Kodiak系列PCIe Gen 4/5/6协议分析仪硬件(包括分析仪主机,以及所有的Interposer)的研发,设计以及测试完全在英国伦敦完成。

SerialTek从PCIe/NVMe Gen 4 分析仪开始首度开始采用其业内首创的全新架构设计,开创了协议分析仪采用高端服务器架构的先河,其分析仪内置12核高性能CPU,区别于传统的协议分析仪软件的“胖客户端”模式(该模式下,所有的分析等功能全部依赖工程师的电脑的性能),该Gen 4分析仪采用Client/Server架构,即“瘦客户端”+高性能server的架构,客户端协议分析软件只是负责产品设置,管理以及显示,所有的需要处理的内容都放在server端进行处理,这样工程师的电脑将获得很大的解放,也不会成为协议分析时的瓶颈。

SerialTek Gen 4分析仪提供千兆以太网管理端口,以及2 x 10GE管理端口,提供36/72/144G Trace Buffer用于抓取PCIe/NVMe流量,内置2TB本地闪存用于快速保存Trace 文件,同时也可以直接保存到连接在分析仪前面板的USB盘或者PCIe盘柜,是全球目前最快的Gen 4 分析仪。

PCIe协议分析仪作为PCIe总线分析的基本工具,不仅仅用于主机,网络,存储系统等各种IT和通讯设备针对PCIe插卡的问题分析,同时也是PCIe/NVMe SSD分析的必备工具。

作为PCIe协议分析革命性创新的领导者,SerialTek公司的PCIe Gen 4/5/6协议分析仪不仅颠覆了传统的PCIe协议分析仪架构设计,大大提高了协议分析仪的性能以及用户的测试效率,改变了用户使用PCIe协议分析仪的习惯,同时,它也提供了超高的灵活性和业内最高的性价比,让更多的公司买得起PCIe Gen 4/5/6协议分析仪。

PCIe协议训练器(PCIe protocol exerciser)是一种用于测试和验证PCI Express(PCIe)总线协议的设备。它可以实现以下功能:

- 仿真测试:模拟PCIe设备与主机之间的通信,以验证硬件和软件的兼容性。

- 错误注入:通过注入错误来测试系统的容错能力,例如丢失数据包、错误的传输速率等。

- 性能评估:测量PCIe总线的吞吐量、延迟等性能指标,以优化系统设计。

- 流量生成:生成不同类型的数据流量,以测试系统对各种负载的响应能力。

- 协议分析:捕获和分析PCIe总线上的数据传输,以便排查问题和优化性能。

- 配置寄存器访问:模拟配置空间中的寄存器访问,以测试设备的配置和控制功能。

总的来说,PCIe协议训练器是一种用于测试、验证和优化PCIe系统的强大工具,可以帮助开发人员和工程师确保其系统在实际部署中的稳定性和性能。